特集記事

半導体業界の話題(第8回)〜 エレクトロニクス業界の発展を牽引してきた「ムーアの法則」はさらに続く⑦〜

厚木エレクトロニクス 加藤 俊夫

今月は、パター二ング技術でも、フォトリソグラフィではないニッチなプロセスを紹介する。

現在はまだ開発中でニッチな感じがするが、成功すれば極めて安価に微細加工ができる技術としてムーアの法則を牽引する可能性を秘めている。

1. ナノインプリント

10nmノード以下の微細加工は、EUV以外には方法がないと思われていたところへ、名乗りを上げたナノインプリントが注目される。

米国Molecular Imprint社が実用化を目指したが成功せず、そこへステッパ開発を諦めたキヤノンがMolecular Imprintを買収して、東芝と協力してビジネス化に挑戦している。

東芝ではNANDフラッシュメモリの生産に用いるべく、検討が進められている。

ナノインプリントの原理は、図1のように古代のメソポタミアまで遡る。伝えられる当時の技術は、王様が粘土板に手紙を書いて地方の部下に連絡する時、王様の署名の代わりに同図のような丸いハンコを粘土板に転がしたそうである。

ナノインプリントもそれと似た原理で、柔らかい樹脂の上にモールド型(テンプレートとも呼ばれる)を押し付けて樹脂を硬化させ、型を引き上げるとパターンが形成されているという簡単な原理である。

そんな簡単な方法でナノメータの微細パターンができるから面白い。

1. ナノインプリントのプロセスの概略

ナノインプリント技術を大きく分けると、光硬化と熱硬化がある。光硬化型は、モールド型の上から光をあてて樹脂を硬化させるもので、熱硬化型は加熱により硬化させるものである。

熱硬化型ではモールド型が熱膨張しパターンの寸法が狂ってくるので、半導体のパターン形成のような用途では、すべて光硬化型である。

当然、モールド型は光が透過できるように透明である必要があり、石英ガラスが一般に用いられる。

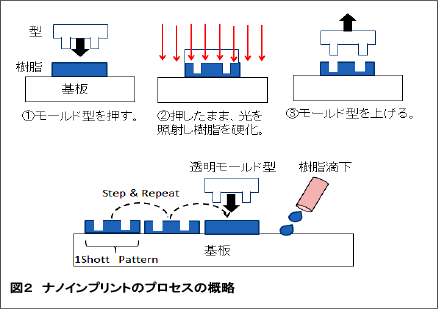

ナノインプリントの基板への転写プロセスを図2に示す。

①基板(シリコン・ウエハ)に樹脂を滴下し、モールド型を押しつける。この樹脂はきわめて粘性が低く、モールド型の細部まで入り込んで行ける。

②モールド型を押したまま紫外線を照射し、樹脂を硬化させる。

③モールド型を引き上げる。

図2の下方の図に示すように、① ② ③の動作を繰り返して、ウエハ全面にステッパ動作を行う。

なお、モールド型の凸部で押したところは樹脂が完全に除去できれば良いが、実際は図2のように薄膜が残り、エッチングで取り除く必要がある。

2. ナノインプリントの優れた点と問題点

優れた点として、

①10nm以下の超微細パターンが得られ、微細加工が簡単にできる。モールド型さえできれば、1〜2nmですら実現したという報告がある。

②LER(Line Edge Roughness)がきわめて小さく、パターンのエッジがスムーズである。

③液浸ステッパやEUVに比べて装置が極めて安価である。

④材料の使用量が少なく、フォトレジストのような大きな無駄がない。

劣っていると思われる点では、

⑤ステッパに比べると、スループットがかなり劣る。

⑥現状では、欠陥密度がステッパより劣っている。

⑦下地パターンとの位置合わせ(Overlay)が、まだ十分ではない。

これらの劣っている点の改善がキヤノンを中心に鋭意進められている。

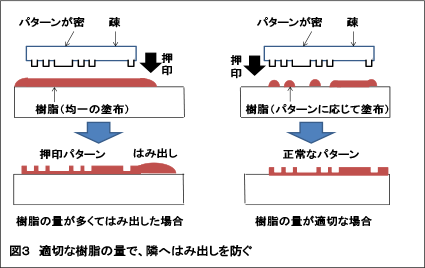

パターンの粗密によって、図3のように樹脂の量を変える必要があって少々厄介だが、実用的には解決している。

なお、モールド型の製作は大日本印刷(DNP)が生産体制を構築して供給可能である。

3. スループット

ArFステッパでは、カタログ上のスループットは250Wafer/Hourとなっている。

いっぽう、ナノインプリントでは、UV光照射で樹脂を固める間はモールド型を動かすことができないので時間がかかり、さらにモールド型の上下動、下地とのマスク合わせ、樹脂の供給にも時間が取られるから、どうしても1ショットに長時間かかってしまい、現在は10〜15Wafer/Hourで、いずれ20Wafer/Hourを目標にしている。

ただし、装置が小型なので4〜6台の装置をクラスタ化して1台にすると、スループットが4〜6倍になる。

4. オーバーレイ(Overlay)

LSIは数十回のパターニングが行われ、前回のパターンとの位置合わせがきわめて重要で、一般には最小パターン寸法の1/4以下の精度が要求されている。したがって10nmのパターンなら合わせ精度は2.5nmとなる。

ナノインプリントの場合、モールド型は石英なので伸縮は少なく十分な精度がある。しかし、ウエハのほうが1000℃近い高温に曝される工程があり、いろいろな膜が表面に付着するので反りや伸縮が発生し、モールド型をこれに合わせる必要がある。

最近のデータではオーバーレイ5nm以下が実現されており、ほとんどの工程に使用できる。

オーバーレイを改善する方法は、モールド型をサイドから押して変形させて、ウエハの歪みに合わせる方法が検討されたが、その他、ウエハの温度を局部的に上げて膨張させる方法なども行われているらしい。

5. パターン欠陥(Defect)

ナノインプリントを生産に導入するために解決すべき最大の問題は、パターン欠陥といわれている。

欠陥が発生する原因は、

①離型の際のモールド型への樹脂付着

②パターンの樹脂はがれ

③樹脂の充填が局部的に不十分か過剰

④樹脂に含まれていた異物

⑤ウエハ表面の異物

などが考えられる。

欠陥を減少させる技術として、樹脂を濾過することにより異物を除く、モールド型を樹脂から離型する時のテクニック、樹脂の改善、モールド型の設計(おそらくほんの少しの形状の改善などが重要だろう)などが行われた。

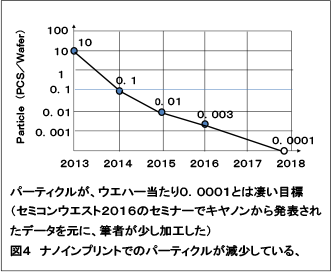

図4はパーティクルの数で、このグラフによると、あと2年で0.0001個/Waferとなり、高歩留まりの生産に十分使用できるレベルとなる。

欠陥起因でモールド型の使用回数が短い(200ウエハ)ので、これを500ウエハに向上することを目標にしているそうである。

6. 解像力

解像力はナノインプリントの得意とするところで、チャンピオンデータでは、1nmというすごいパターンも聞いたことがある。

実際の生産にはそこまでの微細パターンは必要ないが、現状で20nmは楽々実現できており、10nmの生産も実現の可能性が大きい。

LER(Line Edge Roughness)も2nmが報告されており、ステッパより優れた値といえる。

原理的にはナノインプリントではLERは優れているので、はるかに小さな0.5nm程度の値も実現できる可能性があるだろう。

2. DSA(Directed Self Assembly)

1. DSAの原理の説明

DSAとは、日本語で「制限された自己組織化」と訳されているが、その意味は以下の説明で納得していただけると思う。

DSAは、親水性の高分子と疎水性の高分子をつないで1本の高分子としたCopolymerを用いる。PS(Poly Stylene)とPMMA(Polymethylmethacrylate)がよく用いられ、図5のように結合してPS-b-PMMAと表記される場合が多い。

.png)

このCopolymerを基板に塗布して200℃、5min程度加熱すると、図6のような整列したパターンが得られる。

.png)

なぜ、図6のような指紋状の模様ができるのだろうか? 図7のように隣り合った分子のPS同士、PMMA同士が結合して整列する性質があり、その後、PSまたはPMMAをエッチングで除くと、図7右のような指紋状のパターンが得られる。

.png)

この指紋状のパターンでは、半導体生産に用いることができないが、両サイドにまっすぐなガイドを設けておくと、そのガイドにならってまっすぐなLine&Spaceのパターンが得られる。

この両サイドのガイドで制限するのをDirectedといい、すなわちこれがDSA技術である。

2. Grapho Epitaxy

DSA技術でパターンを作成するには、Grapho EpitaxyとChemo Epitaxyの二通りの方法があるが、ここではGrapho Epitaxy法を説明する。

図8はプロセス手順で、①基板にフォトレジストでガイドとなるパターンを形成し、加熱ベーキングしてレジストを硬化させる。次いで図の②、③のようにCopolymerを塗布して加熱すると、ガイド・パターンに沿って何本かの線が形成される。④PMMAを剥離すると図のようなラインが残る。

.png)

このようにガイド・パターンで制限されたスペースに何本かのラインを形成するのがGrapho Epitaxy法によるDSAである。

フォトレジストでガイド・パターンを作るのは微細パターンではない従来のリソグラフィ技術で対応できる。

すなわち、粗いパターンをフォトリソグラフィで行い、微細なパターンはDSAで行えるわけである。

3. DSAの現状と問題点

最大の問題点は欠陥といわれている。典型的な例を図9に示す。

.png)

点状の欠陥は、材料またはプロセス中の異物が原因である可能性があり、図の右の場合はプロセス上の問題なのか、材料のCoPlymerに異常な高分子が含まれていたのか、基板上に異物が載っていたのかなど、さらに解明し対策する必要がある。

4. DSAのまとめ

ナノインプリントの装置はステッパに比べて安価だが、DSAの装置はそれよりさらに安価だと思われる。

DSAは、欠陥の問題が解決すれば、コストが安いためすぐに生産に用いられる可能性があるが、現状は技術の進展を見守っている状況で、いつ生産に導入されるか予測が難しい。

DSAで得られるパターンは、Copolymerの長さ次第で微細加工が可能なのも魅力である。

ただし、DSAは直線のLine&Spaceしかできないので、いろいろなパターンを自由に作成するRandom Layoutができない欠点もあるが、大部分のLSIには対応できる。

以上、今月はフォトリソグラフィを用いない微細パターニングの方法について報告した。

ナノインプリントとDSAは、共にまだ研究開発段階であるが、手軽なプロセスで安価に微細加工ができるので、LSIの性能向上とコストダウンに寄与すると期待される。

来月は、CMOSLSIがFinFET構造で3次元化され、さらにはナノワイヤLSIが来年あたり生産に入るといわれているので、それらの技術を紹介する予定である。

![【見どころ】「第14回 高機能素材 Week[大阪]」 【見どころ】「第14回 高機能素材 Week[大阪]」](https://jpcb.jp/upload/pickup/M/02757_1776314842.png)