特集記事

半導体業界の話題(第9回)〜エレクトロニクス業界の発展を牽引してきた「ムーアの法則」はさらに続く⑧〜

厚木エレクトロニクス 加藤 俊夫

1. はじめに

ムーアの法則を推進する中心となるパター二ング技術を解説してきたが、微細化を進めると、デバイスの構造の改革も重要テーマとなってきた。CMOSLSIの構造はどのように変遷するであろうか。今月と来月に取り上げ、本連載を締め括ることにする。

2. ショートチャンネル効果の抑制

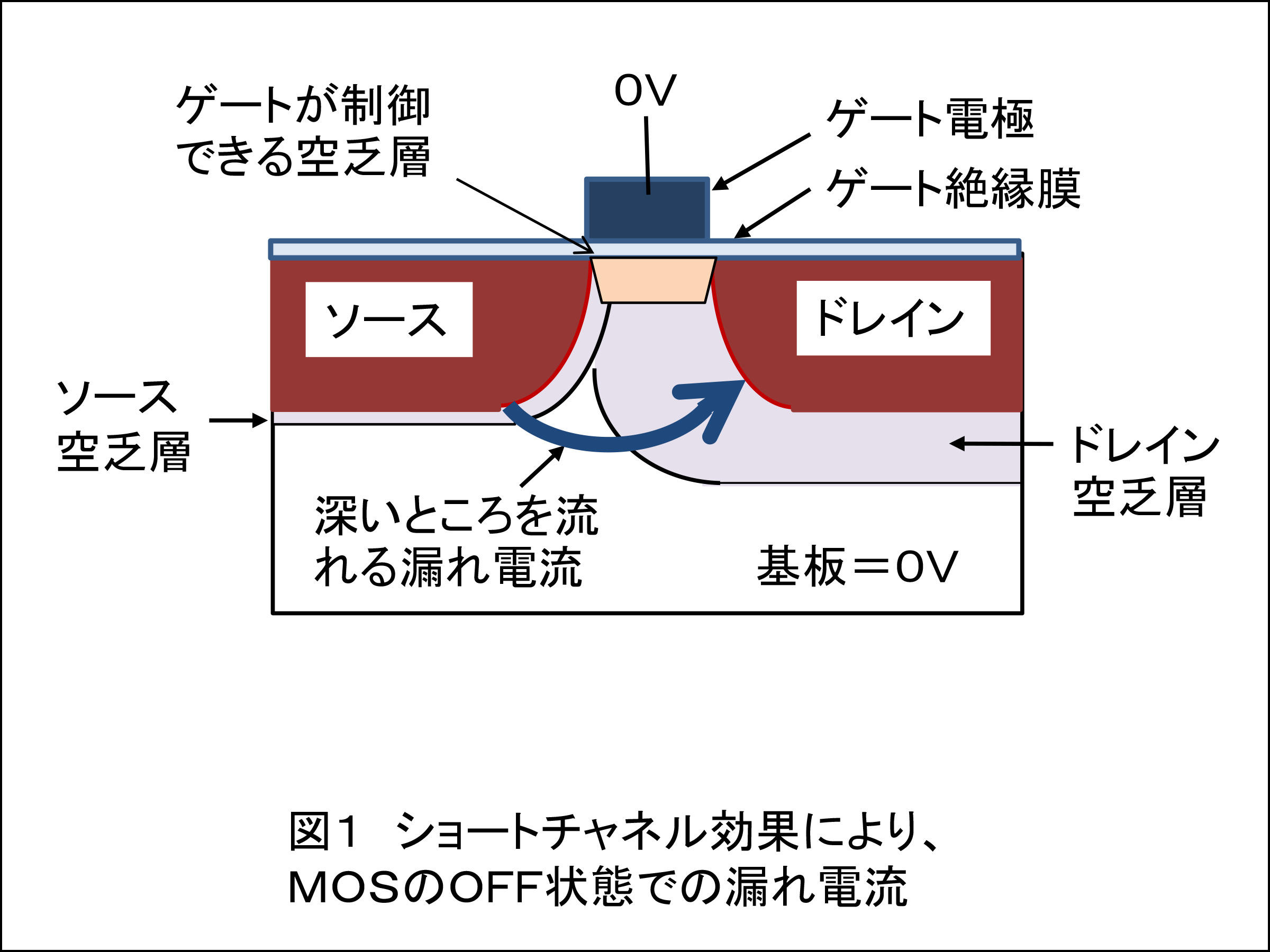

LSIの歴史は、ショートチャンネル効果との戦いだったといわれることもある。ショートチャンネル効果といっても余り馴染みのない方も多いと思われるので、図1を見ながら簡単に説明しよう。

LSIのパターンの微細化がどんどん進むと、本来は比例縮小則により深さ方向も縮小されるべきであるが、ソース・ドレインが極端に浅くなると寄生抵抗が大きくなり、電極のコンタクトもとりにくくなって限界がある。すると図1のようにゲートの電界が深いところまで及ばず、ドレインの電界によって空乏層が広がってしまい、本来はOFFの時にもソースからドレインに電流が流れてしまう。

これがショートチャンネル効果である。空乏層の成長を防ぐため、チャンネル部分の濃度を高くする斜めイオン注入や、Extention構造が利用されたが、10nm時代になると不十分になってきた。

根本的な解決策として、LSIの構造をFinFETに変えてしまうことが行われ、今や最先端のLSIはすべてFinFETになって、ショートチャンネル効果はほぼ完全に抑えられている。

3. FinFETの採用

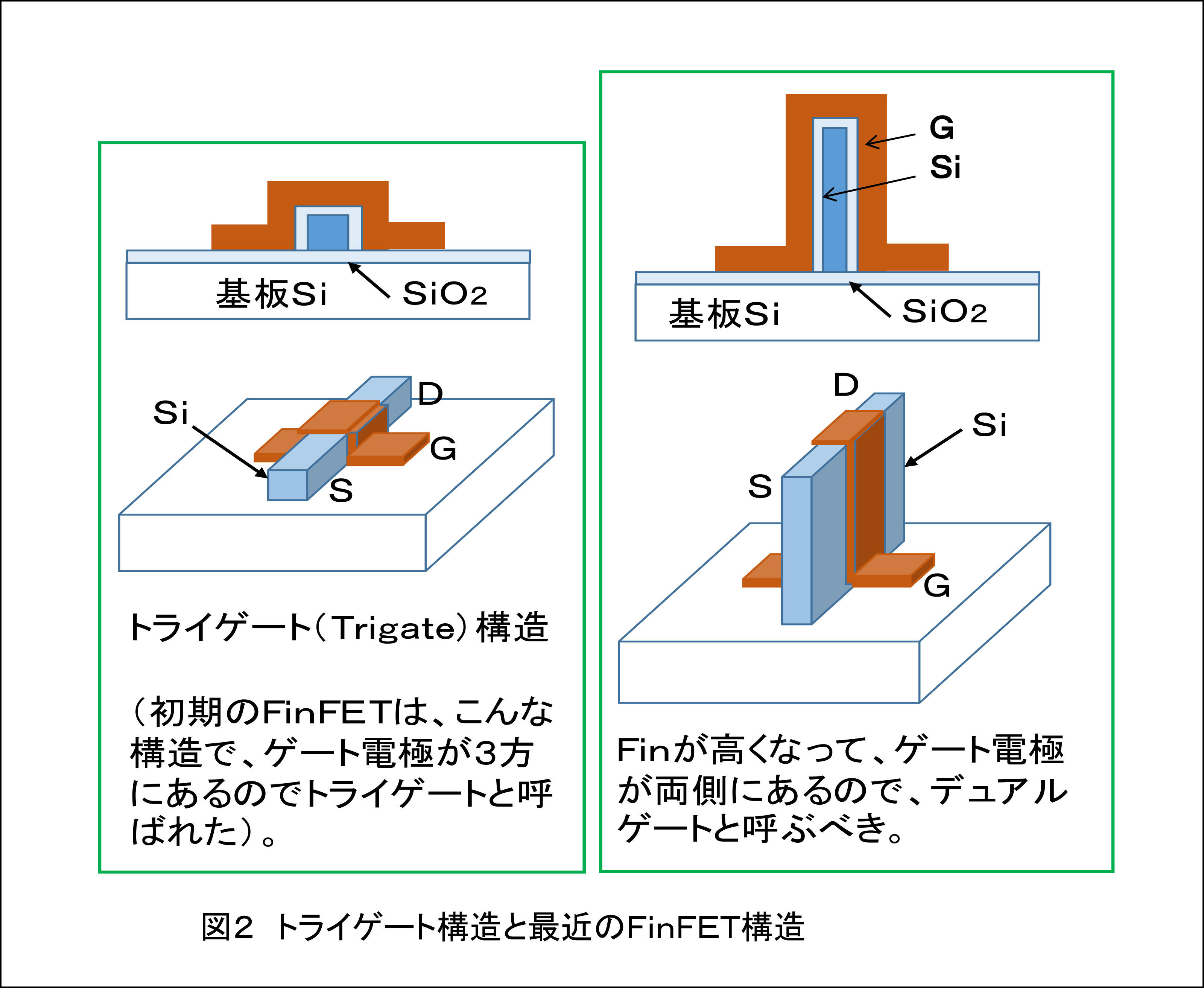

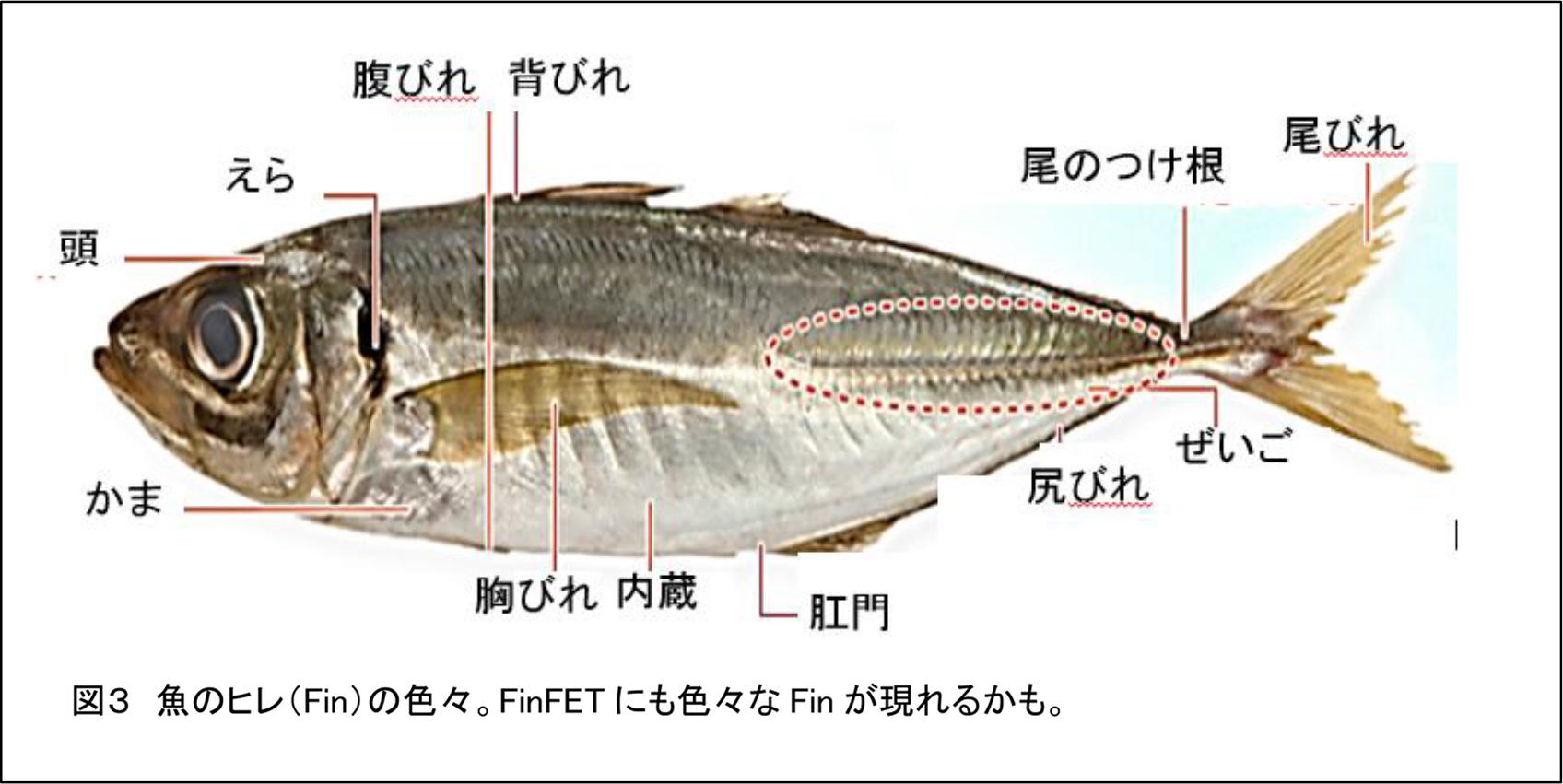

最初に生産されたのは、図2左のトライゲート型のFinFETであった。Finとは図3のような魚のひれのことで、バー状のSiが「ひれ」のように両側に出ていることからFinFETと名付けられた。

数年前、インテルが22nmプロセスで生産をはじめた時は、図2左のようにSiの側面と上面にゲートがあったので、Tri‐Gate(3面ゲート)と呼ばれた。

バー状のSiの3面をゲートが囲んでおり、ゲートの電界がバー全体を制御することができて、ショートチャンネル効果が抑制され、リーク電流の発生がほとんどなくなった。その後、電流を多くとる必要からSiバーはどんどん背が高くなって、図2右のようになり、Tri‐Gateというよりも、左右両面ゲート(Double Gateというべき)構造になり、通常は単にFinFETと呼ばれている。

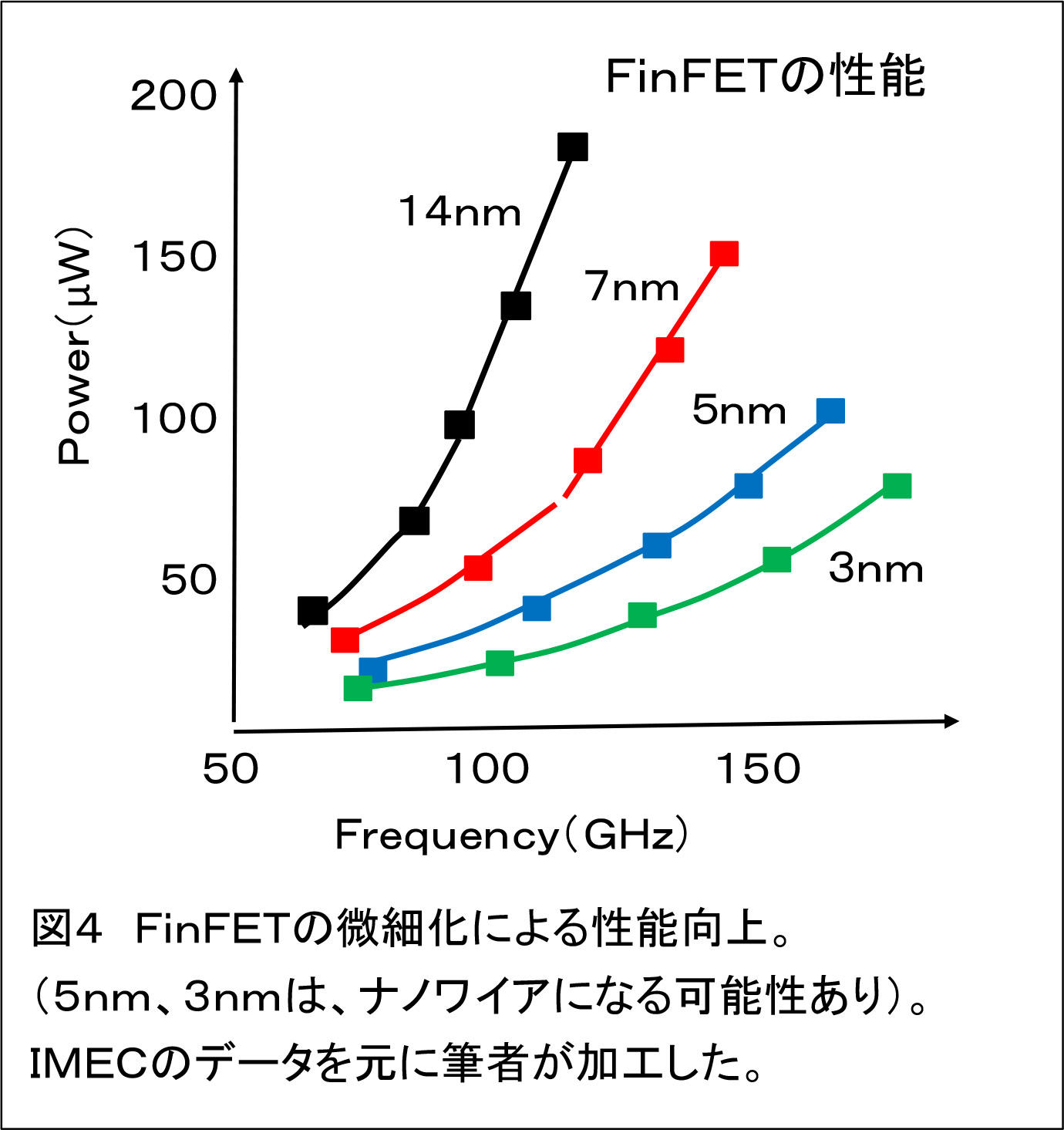

FinFETの微細化が進むと、集積度が上がるだけでなく性能も向上する。比例縮小則に100%従うことは無理だが、消費電力と動作速度の関係は、図4のように向上する。

1. ナノワイア(GAA)へ移行か?

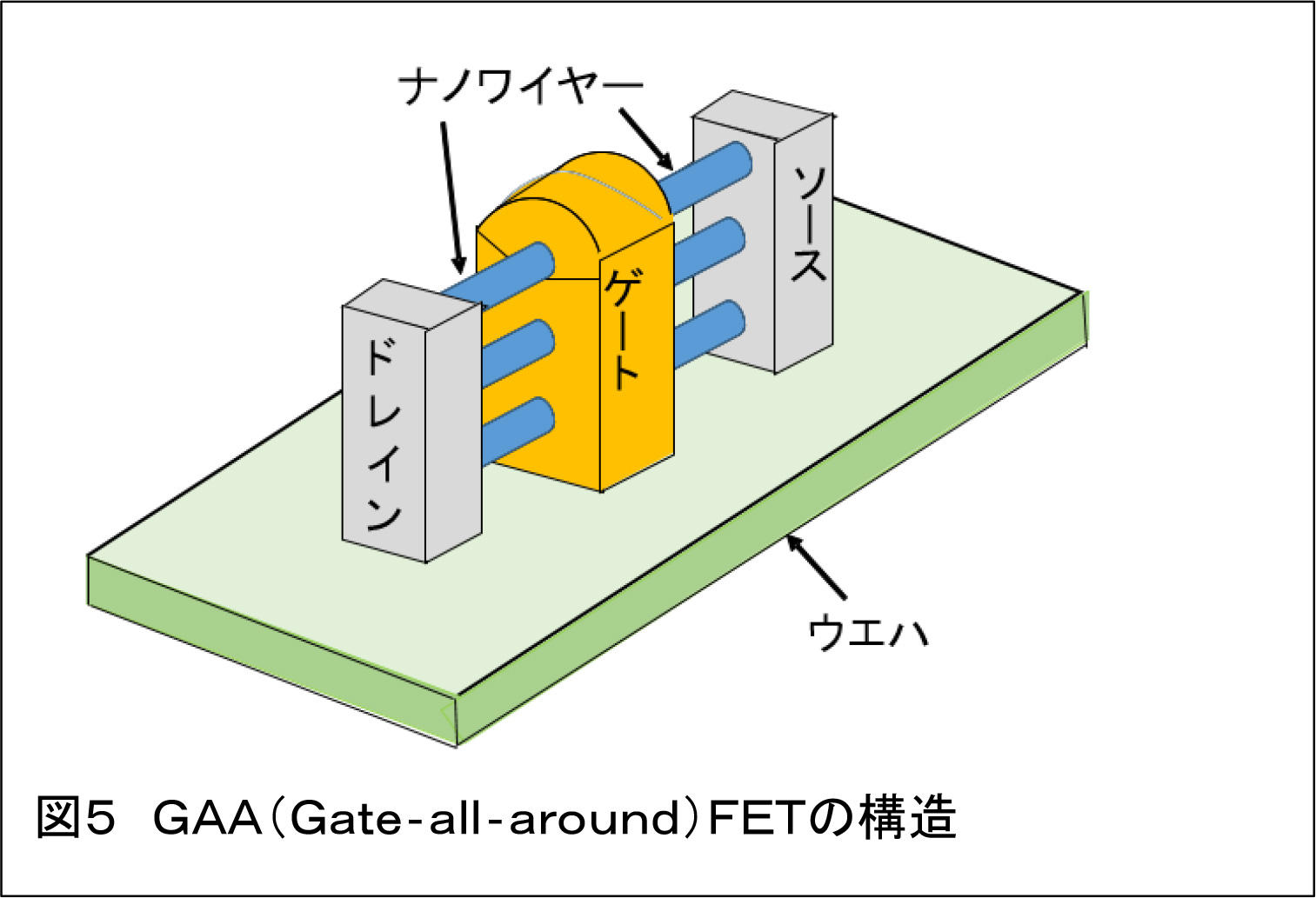

FinFETは、短チャネル効果によるリーク電流低減やゲート電極の制御性を高める技術を進化させたが、5nm世代ではGAA(Gate all around)への移行が検討されている(5nmでは、まだFinFETだという意見もあるが)。

GAAは、図5のように、ナノワイア状のSiチャンネルをゲート酸化膜とゲート電極がぐるりと取り囲む構造になっている。

Siナノワイアは、直径10nm以下(角型もある)が考えられているが、年々微細になると思われる。ナノワイアはゲートからの制御性は優れているが、微細なので電流が多く流せないので、図5のように数本のナノワイアを重ねた構造が考えられている。

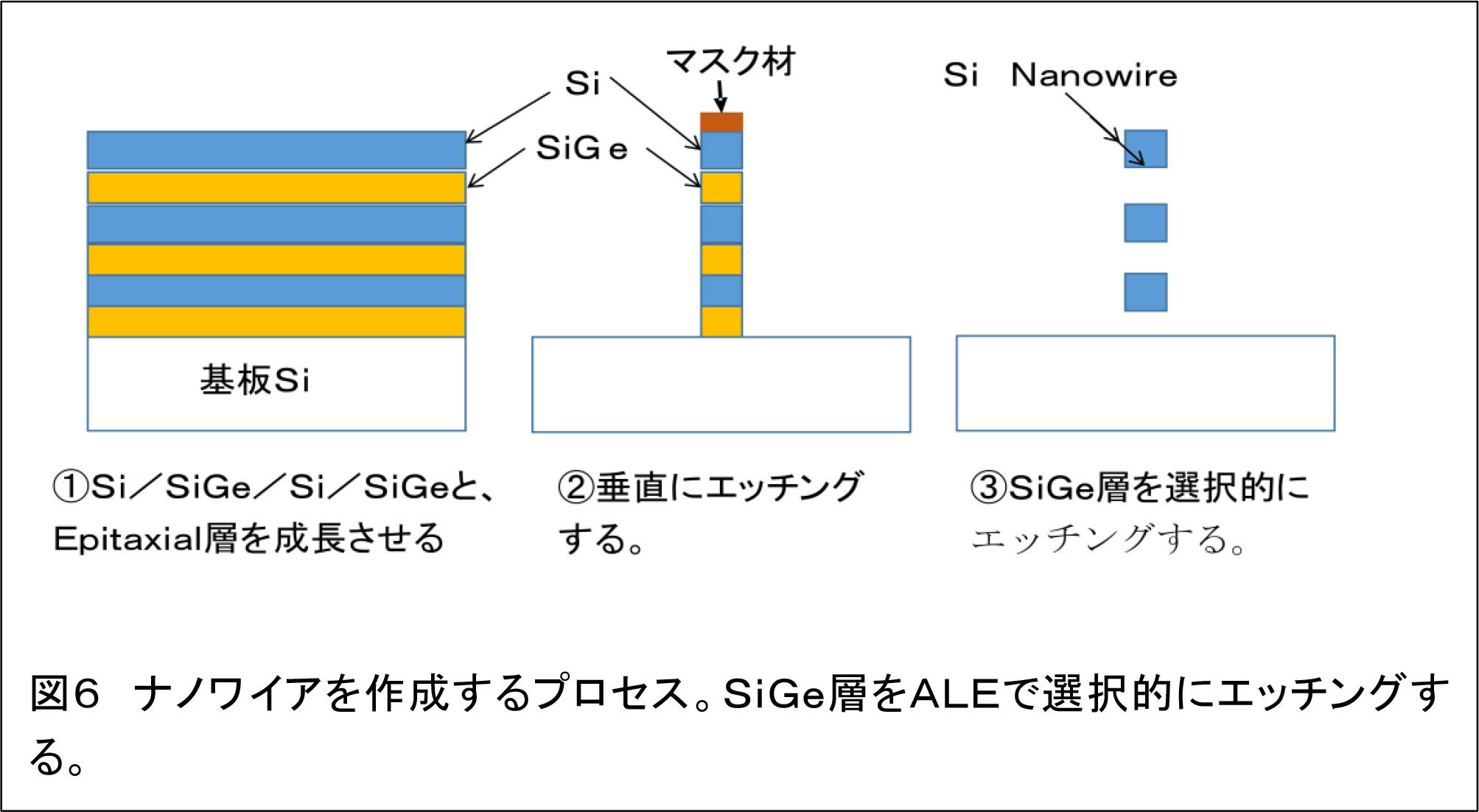

量産化を考慮すると、このようなナノワイアをウエハ上に規則正しく並べる必要があり、どんな方法でアクロバット的な構造を作るのだろうか?

レポートによると比較的簡単に書いてある。すなわち、図6のように、Si/SiGe/Si/SiGeとEpitaxial成長させ、パター二ング&エッチングしてナノワイアになる部分を壁のような構造にし、ソースとドレインの電極を設けて固定した後、SiGe層を選択的にエッチングすれば、Siワイアが残って多層のナノワイアが完成する。と、簡単に書いたが、SiGeのエッチングには、ALE(Atomic Layer Etching)という原子を1層ずつエッチングする手法が用いられ、さらにゲート酸化膜とゲート電極をナノワイアの回りに形成するには、ALD(Atomic Layer Deposition)が用いられている。まさにプロセス技術の粋を集めたデバイスの製法といえる。

IBMのGAAに関する試作レポートによると、寸法はナノワイアのピッチが30nm、チャンネル部分の幅と高さは10nm、ゲート長は10nm、OFF状態の電流値Ioffは100nA/µm(VDD=0.68V)以下となっている。

チャンネル部分は、ドーピングなしにするとキャリアの移動度が大きくなって好ましいが、Vt(Threshold Voltage:閾値電圧)の制御が難しい。

ゲート金属の仕事関数を考慮して、PMOSとNMOSに適したゲート電極を形成すればよいが、プロセスが複雑になるので、ナノワイアを製作する時にドーピングしてVt値のアジャストを行うそうである。

2. さらにナノシートで電流値をアップ

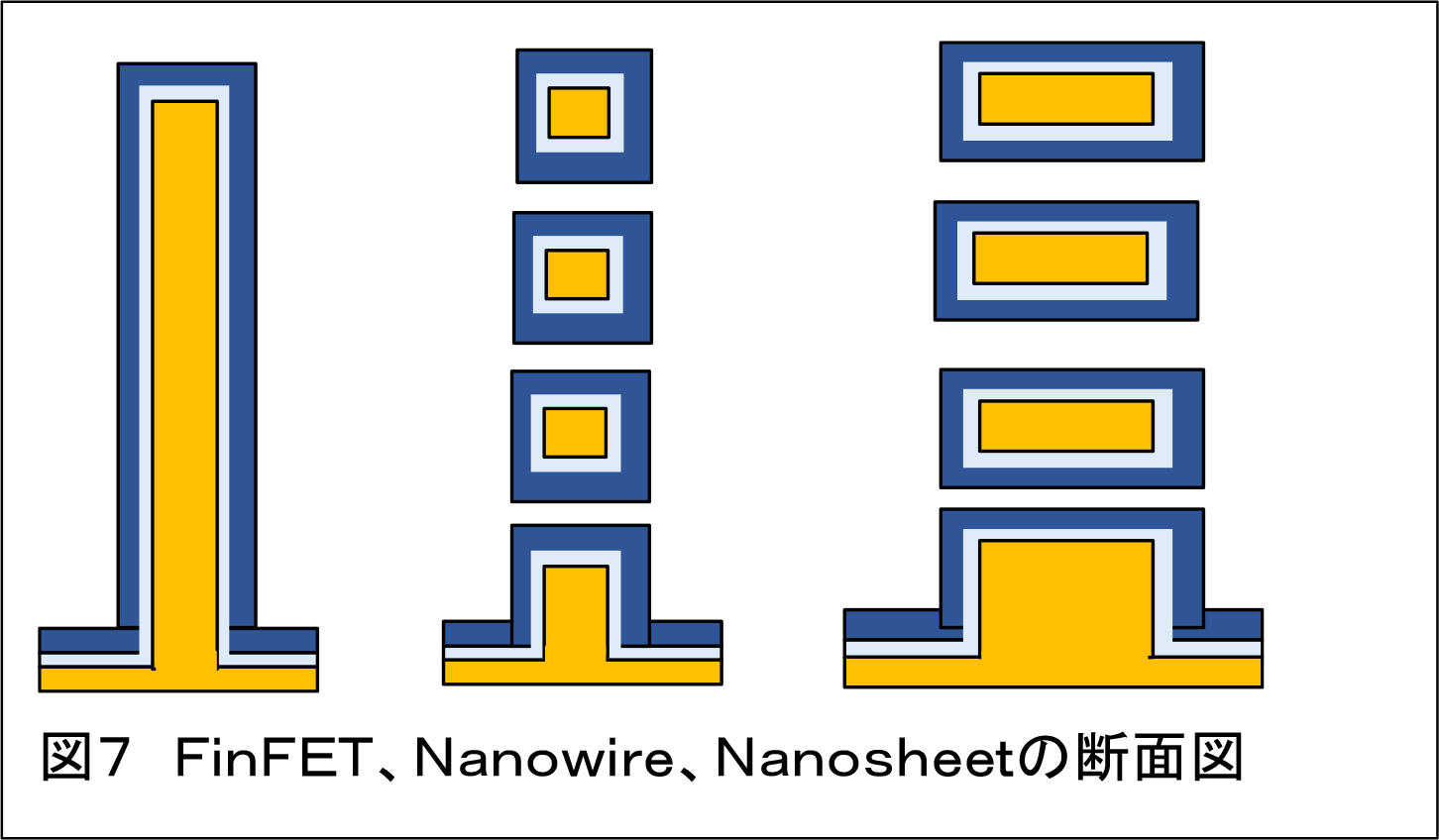

ナノワイアと似たような構造で、ナノシートも話題になっている。ナノワイアと同じように、シートの回りをゲート絶縁膜とゲート電極が取り巻いている。ワイアよりシートの方が断面積は大きいので電流を多く流せる。ただし、トランジスタの面積はナノワイアより大きくなり、集積度は劣る。

FinFET、ナノワイア、ナノシートの断面図を図7にあげておく。ナノワイアやナノシートでは、10〜5nmと微細な上に、側壁だけでなく下側(裏側)にも膜をデポジットしなければならないコンフォーマル(どんな表面にも裏面にも回り込んで膜が付着すること)が必要になるので、かなりプロセスは厄介である。しかし、数年後には量産していると考えられている。

IBMの発表によると、5nmのナノシートでは、10nmのFinFETに比べて消費電力は75%も削減できたそうで、デナードの比例縮小則は、まだ生きているようです。

3. 縦型ナノワイアへ移行するのか?

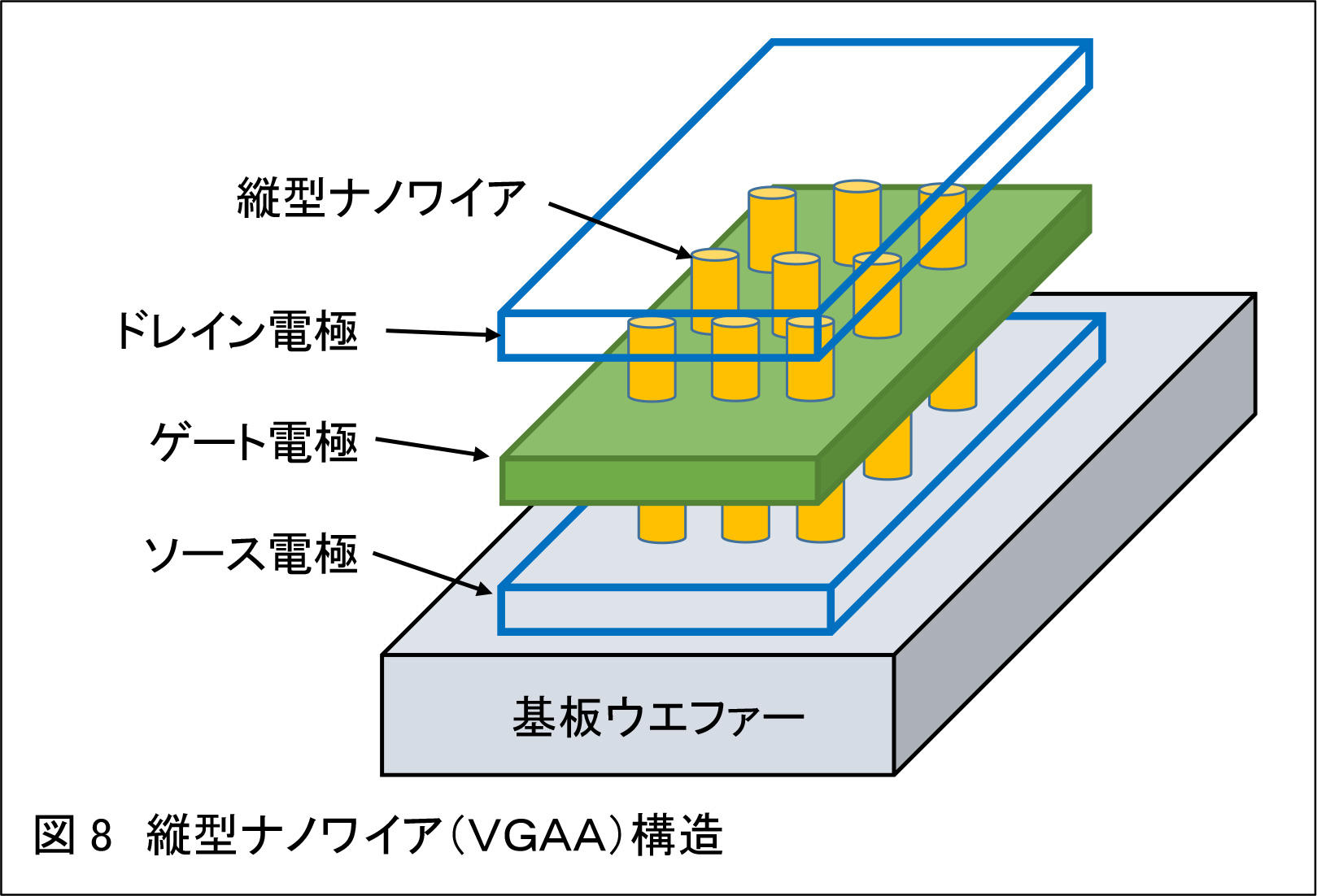

これまで見てきたナノワイアは、水平方向にナノワイアを並べる構造だったが、その先のMOS構造として縦型ナノワイア(VGAA:Vertical Gate all around)が検討されている。

図8のように、ちょうどお花の剣山か、あるいは、やまあらしの毛のように、ウエハ上に垂直にSiナノワイアが林立している構造である。

縦型ナノワイアは、数年以内に実用化されるという意見もあり、ITRS2015ロードマップでもそのように書いてあったが、水平ナノワイア時代が少なくとも数年は続くだろうから、それを飛び越して縦型がすぐに実用化されるとは考えにくく、筆者はかなり先の話だと思っている。

Siの柱を立てるだけならいろいろな方法が考えられるが、図8のようにソース・ドレイン・ゲートの電極をつけて、CMOS化のためにPMOSとNMOSを隣合わせに作るのは簡単なプロセスとは思えない。かなりの工夫が要ると思われ、今後の研究開発の進展が楽しみである。

ムーアの法則は、年々LSIの集積度が向上するという意味であるが、これまでの歴史は、微細化により集積度が向上するとともに、性能も向上した。

ところが、今月述べたFinFETからナノワイヤへの進展は、集積度の向上はあまり見られず性能の向上に重点が置かれている。性能の向上のためには、異種材料の検討が精力的に行われており、来月取り上げる予定である。集積度の点だけをいえば、NANDフラッシュの3次元化に頼ることになる。

来月はムーアの法則の最終回として、それらの話題を取り上げたいと思っている。

![【見どころ】「第14回 高機能素材 Week[大阪]」 【見どころ】「第14回 高機能素材 Week[大阪]」](https://jpcb.jp/upload/pickup/M/02757_1776314842.png)