特集記事

半導体業界の話題(第5回) 〜エレクトロニクス業界の発展を牽引してきた「ムーアの法則」はさらに続く④〜

厚木エレクトロニクス 加藤 俊夫

1. はじめに

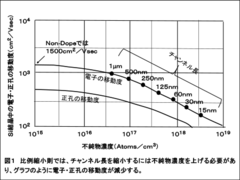

1972年にIBMのデナードが比例縮小則(Scaling Rule)を提唱し、MOSICのパターンを微細化するにしたがい、電流と電圧を下げることができ(すなわち消費電力が下がり)、動作速度は向上し、集積度も増えると言う願ってもないルールである。

従ってLSIの性能向上と集積度向上を同時に達成できる微細化競争が始まったわけである。LSIの微細化を行う時のルールと、得られる特性を図1に示す。

.png)

ところが、パターン寸法が30nm以下まで微細化が進むと、多くの困難な問題が顕在化してきた。

ゲート酸化膜も1nm程度まで薄くする必要があり、この程度の薄さになると、MOS動作に関係のないトンネル電流が流れて消費電力が大きくなってしまうことになった。

今月は、このゲート酸化膜問題を取り上げる。

2. トンネル電流とは

ゲート酸化膜がどんどん薄くなって1nm(10Å:オングストローム)程度になると、絶縁物のはずの酸化膜(SiO2)が絶縁物でなくなってしまい、酸化膜中を電流が流れる。

これを説明するには、どうしても大嫌いな量子論をもち出す必要がある。

光は回折現象などから波と思われ、固有の波長や振動数をもっている。

ところがアインシュタインが光電効果を説明するのに、光は粒であるといいだし、今では「波のようでもあり、粒のようでもある」ものとなっている。

いっぽう、電子は、原子核の周りを回っている粒であると考えるが、ド・ブロイが電子も回折することを見出し、粒でもあり波でもあるとなった。

電子顕微鏡など、電子の波の性質を利用した機器が使われている。

要は、原子程度の微細な現象は、我々が日常接している現象とは異なっており、波であり粒であると言われると、どんなものかを表現する方法がないわけである。

さて、そこで1nm以下の薄い酸化膜の場合を考えると、電子が粒と考えるとボールを壁にぶつける図2のように跳ね返ってくる。

.png)

ところが電子が波ならどうだろうか? 壁の片方から大きな声で叫ぶと、薄い板なら反対側で聞こえる。

これと同じように電子は壁をすり抜けて反対側に出てくる。これをトンネル効果と呼んでいる。

図3は、トンネル電流と酸化膜の厚さの関係のグラフで、30Åと10Åでは3桁近い差があり、10Å(すなわち1nm)程度に薄くなると途端に大電流が流れてしまう。

.png)

最先端のLSIを開発したのに、トンネル電流が大きいため消費電力が大きく発熱が抑えられなくて生産を中止した例もあると聞いている。

3. 高誘電率膜の採用

ゲート酸化膜を薄くする理由は、ゲート電極とチャンネルとのキャパシタンスを大きくしてチャンネルを流れる電流を大きくするためである。

そこで、このキャパシタンスを大きな値にするため、高誘電率(High−kと呼ばれる)の絶縁膜を用いる検討が行われた。

図4に各種のHigh-k膜をあげた。初期の頃は、k=7のSi3N4が用いられたが、さらに、TiO2、Al2O3、La2O3、ZrO2などが検討され、現在はk=20程度のHfO2系の材料が一般的に用いられている。

SiO2のk値は4なのでHfO2はこれの5倍であるから、5nmの厚さがSiO2の1nmに相当する。この関係をEOT(Equivalent Oxide Thickness)1nmといっている。

5nmの厚さならトンネル電流の心配はまったくいらない。

.png)

4. Metal Gate

MOSが最初に生産された1970年頃は、ゲート電極にはアルミニウムが用いられ、イオン注入が一般化されていなかったので、ソースとドレインを拡散で形成した後にゲートを作成していた。

イオン注入が使えるようになり、ゲートをマスクにしてソースとドレインを形成して相互の位置合わせがセルフアラインできるようになり、1000℃のアニールに耐えるようにゲート材はポリシリコンになった。

ところが、ポリシリコンは電極の金属として用いられてきたが、半導体でもあって、電界が掛かると図5のように空乏層が発生する。

.png)

このため、せっかくゲート絶縁膜を薄くして容量を大きくしても、ポリシリコンの空乏層が加わっては容量が減少してしまう。

これを避けるため、ゲート電極を金属にする必要がある。絶縁膜がhigh-kで、電極がMetal Gate構造を、HK-MGと呼んでおり、LSIの一般的な構造となっている。

ところが、ゲート電極をCuやAlなどの金属にすると、1000℃のアニールに耐えられないし、HfO2膜も結晶化がはじまって面白くない。

そこで、図6のようなゲートラストと呼ばれるプロセスが用いられている。

.png)

すなわち、いったんポリシリコンゲートで、ソースとドレインへのドーピングを行い、ついでポリシリコンを剥離して、HfO2膜と金属に置き換えるわけである。

金属としては、TiNが主に用いられていると思われるが、TaC、TaN、NiSiなどの名前も聞かれる。

いっぽう、このゲートラストは非常に手が込んだプロセスでコストアップになるので、従来のプロセスに近いゲートファーストも行われている。

ただし、ゲート電極の金属はMOSのVth(MOSがONになるゲート電圧)を調整するため、PMOSとNMOSで異なった金属が採用されるが、あまりに複雑な話になるので省略する。

5. 酸化膜に関する信頼性問題

1. NBTI(Negative Bias Temperature Instability)

LSIの信頼性は、一般の電子部品と同じように、使いはじめた初期不良と、長期間使用して寿命と見なされる不良があり、通常に使用している最中の不良はかなり少ない。ところがMOSのNBTIと呼ばれる不良は使用中にMOS特性が変動するという問題である。

ゲート電極に対し基板の電位が負の状態でチップの温度が上昇すると、P型トランジスタのVthの絶対値が徐々に大きくなる。負バイアスが印加されない状態では変動した特性が急速に回復する。

この現象のメカニズムは完全に解明されていないようであるが、図7のようにSi-SiO2界面にあるSi-Hの結合が切れてここに正の電荷が存在するように考えられ、MOSのVthが高くなってしまう。

.png)

2. NANDフラッシュ・メモリの寿命

薄い酸化膜に関連して少し横道に入ってしまうが、NANDフラッシュ・メモリについて一言。

NANDフラッシュは、薄膜を積み重ねる3次元化が進み、今や集積度の大きさではDRAMなどをはるかに引き離してムーアの法則を牽引する中心デバイスとなっている。

記憶するメカニズムは、周りを絶縁物(SiO2)で囲まれた浮遊ゲート(Flouting Gate)に電荷を貯めるわけで、電荷はSiO2膜に高電圧をかけて電子が通る。

このため、長年の内には、図8のようにSiO2膜に欠陥が発生して誤動作を起こすことになり、書き換え回数があまり多くは期待できない。

したがって、あまり頻繁に書き換えしなくても良いような用途に使われている。

.png)

今月は、薄い酸化膜を取り上げたが、来月は結晶に歪を与えてCMOS特性を改善する方法、再来月はFinFETを取り上げる予定である。乞うご期待。