特集記事

プリント基板のレイアウト設計と製造をシームレスにつなぐインテリジェントなDFMソリューション

メンター・グラフィックス・ジャパン(株) 吉田 昌広

1. はじめに

近年、製品のライフサイクルが短くなってきている状況において、新製品をより早くマーケットに投入することが求められている。

いっぽう、大規模化かつ複雑化する半導体、ソフトウェア、回路などの増加により、設計完成度の不足、設計引継ぎや量産立ち上げの遅延が発生し、設計→新製品導入→試作→量産への移行から量産安定化までのリードタイムを併せたTime-to-Marketの短縮が図れない場合が多くなってきている。

2. NPI(新製品導入)プロセスの重要性と課題

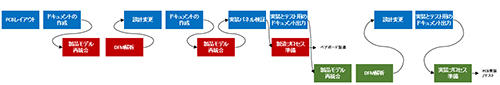

プリント基板(PCB)の新製品導入(NPI)は、製品モデルの作成を目的とするレイアウト設計ドメインから、高品質でコストを抑えた製造プロセスの定義と運用を重要視する製造ドメイン(基板製造、実装、テストで構成される)へ移行する非常に重要な段階である。

PCBの製造段階への移行時に直面する問題の多くは、製造プロセスか歩留まりに影響を及ぼす。

PCB実装に関わる問題が原因で廃棄、もしくは大幅な手戻りを余儀なくされることもあり、そのような場合にはレイアウト設計自体を見直し、製造プロセスにあった製品に設計し直す必要性が生じてしまう。

PCB実装サプライヤで発見された問題点はレイアウト設計者にフィードバックされ、DFM解析結果に基づいて製造性を考慮した修正を行う。図面に不備があった場合などは特に、製造可能な設計に辿り着くまでにこのやり取りを何度も繰り返すことになる。

図1 NPIフローの課題

3. 設計と製造間のデータ連携における課題

PCB設計者がPCB製造企業に送る図面とデータパッケージには、製造に必要となる様々な要件仕様が含まれている。

通常の場合、BOM(部品表)、ガーバファイル、エクセロンフォーマットのドリルデータ、部品配置情報ファイル、図面、ネットリストなどといった形式の異なる多数のデータが送られてくるため、製造側でエンジニアが「製造製品モデル」を再構築するまでには数々のデータ処理と再コンパイルの作業を行わなければならず、多くの手間が掛かる。

製造企業は、PCBのレイヤを個々に登録して重ね合わせ、必要な属性をすべて定義し、レイヤ構成と材料の種類を設定し、図面による検証作業を行う。

その後、製造プロセスに応じた正しいデータを抽出して、ようやく装置のプログラミングとツーリングへ進むことができるようになる。

同様に、PCBの実装とテストの前にも多くの段階を踏まなくてはならないが、ここでもデータを変換して検証する必要がある。

部品配置情報にBOMやネットリストを統合し、テストポイントを挿入する。BOMのフォーマットは部門や顧客ごとに異なり、テキストの場合もあればExcel形式の場合もあり、書式も統一されていないことが多い。

製造と実装、テストの準備はどれも非常に時間がかかるものであり、データの変換ミスや図面の解釈ミスといったリスクを常に孕んでいる。

だからこそ、今まで通常とされてきた前述のやり方では、製品NPI 作業の大半がプロセスエンジニアリングのタイミングまで「持ち越され」、きわめて非効率なものとなってしまう。

4. ODB++の活用

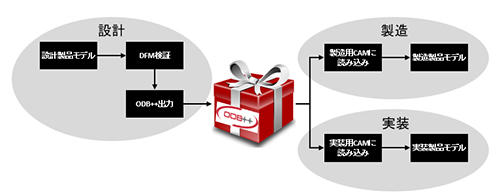

ODB++は、PCB設計および実装企業間のグローバルなデータ交換を統合的に実行するPCB製造用の完全なデータ交換フォーマットである。

ベアボードや実装完了後のPCB情報を正確に定義した製品モデルがインテリジェントにデータ化されており、データの再コンパイルを行うことなく、プロセス準備段階に直接データを供給できる。

図2 ODB++データによる設計・製造間のデータ交換

これにより、設計意図を読み違えるリスクが軽減され、設計から製造全体のリードタイム短縮に貢献する。ODB++はオープンフォーマットであり、ODB++ Solutions Alliance(https://www.odb-sa.com/ja/)の登録メンバーなら誰でも、PCB設計から製造にいたるフロー全体を通してのODB++フォーマットの利用体験や実装のベストプラクティスなどの情報、ODB++に関するアドバイスやアイディアを交換できるようになっている。

5. NPIソフトウェアに求められること

基板製造企業と実装企業の能力を総合的に判断しながら、初回のリリースプロセス中に設計を最適化する方法を見つけることは、NPIプロセスを成功に導くために欠かせない要素である。

NPIソフトウェアに求められるのは、単に間違いを見つけるだけでなく、選択した製造プロセスに含まれるさまざまな課題や制限を理解したうえで、目的に最も適したトレードオフの決定を下せるように製品責任者を支援する機能である。

理想的な設計要件や製造プロセスの限界を定義する技術も重要である。

正しい制約ルールが適切に割り当てられるように設計データを分析し、製造許容差を制約に適用し、DFMルールエンジンがこの製造許容差を自動的に考慮して、DFMルールに適合しているか違反しているのかを判断できなければならない。

Mentor, a Siemens Business(以下メンター)が提供する『Valor NPI』は、DFM(製造を考慮した設計)の考え方に基づき、設計段階で製造と実装の問題点を検証、解決するプリント基板(PCB)新製品導入ソリューションである。

PCBのデザインレビューをシステム化し、設計者の作業効率化、設計手戻りの削減、製品全体の品質向上、短納期化に貢献する。

6. DFM解析の自動化

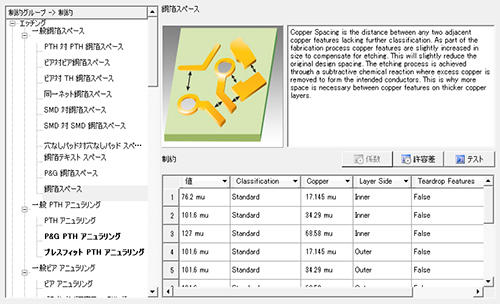

『Valor NPI』は、独自のシステムロジックを用いてDFM 解析を自動化する機能を持っている。

インテリジェントな設計データを用いてPCBの分類を自動決定し、PCBテクノロジと製造制約の組合せに基づいて最も適切な品質DFM 解析を実行する。

図3 PCBテクノロジに応じたDFMルールの自動選択

たとえば、基板製造DFM解析では各層における銅箔の重量が重要となるが、これは使用されている銅箔の重量によって適用するエッチング補正が変わるからである(内層と外層で違うものになる)。

15gの銅箔でできた内層で75μmの間隔は許容範囲であるが、同じボードの外層には30gの銅箔が使われているため100μmの間隔が必要となる。

さらに、積層ビアで構成されるPCBには、単層の回路基板とは異なるDFM ルールを適用する。

『Valor NPI』は、こうした特性に自動的に対応することで設計データの分析とルールの選定に関わる工数を削減し、すべてのユーザに一貫して理想的な環境を提供する。

また、設計要件やプロセス要件を収集して管理する作業が容易になり、紛らわしい構成要件や段取り要件を排除することが可能となる。

PCB設計者は社内の設計ガイドライン要件と業界のガイドライン要件を満たす責任を持つが、このソリューションを使えば、DFM要件のあらゆる側面に対応できる。

設計と製造の間の技術的な窓口となることが多い製造エンジニアやNPIエンジニアは、複数のプロセスにまたがる製造要件やサプライヤの要件を容易に評価できる。

一方EMSベンダは、製造を成功させるために、製造ラインプロセスや複数の場所に対して製造要件を評価できる。

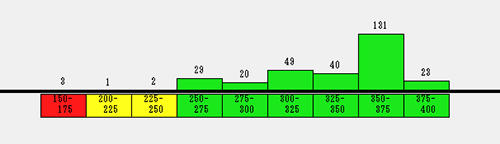

7. DFMヒストグラムによる歩留まり改善可能性の評価

DFM解析は、「合格・不合格」で判定するデザインルールチェック(DRC)とは性質が異なる。製造工程で問題となるのは歩留まり、品質、製品の信頼性である。結果は深刻度によって「製造不可能」から「問題無し」に分類され、中間にあたる部分は歩留まり改善の可能性を示している。

この部分は試作では問題にならなくても、量産の妨げとなることがある。

『Valor NPI』ではヒストグラムにより閾値の範囲ごとに検出数を表示し、解析結果の分布を確認できる。

図4 DFM解析結果のヒストグラム表示

8. 「シフトレフト」DFMによるコンカレントなPCB設計プロセス

PCB設計の各マイルストーンで段階的にDFM解析を実施することは効果的であり、競争上の優位性を高めることができる。

設計とリリースの各プロセスにおける担当者が問題を把握して早期に対処することで、設計が下流に進んだ後に問題が発生する可能性を排除し、手戻り時間を削減することが可能となる。また、設計者の製造への意識を高める効果も期待できる。

図5 設計の各マイルストーンで行う段階的なDFM解析

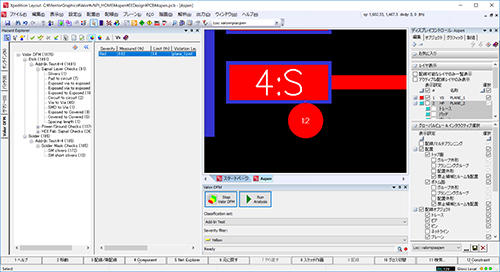

PCB設計プロセスと同時進行でDFM解析が可能な環境の実現には、理想的にはDFMソフトウェアを電子設計(EDA)ソフトウェアと緊密に統合して、設計者がレイアウトツールの環境内で基本的なDFM解析を実行して結果を確認できるようにする必要がある。

メンターの『Xpedition xPCB Layout』では、『Valor NPI』を使用したDFM検証と結果確認をすべて同一画面で実行できるため、設計者が『Valor NPI』アプリケーションの操作を習得していなくても、『Valor NPI』のDFM解析を利用できる。

図6 Xpedition用のValor DFMアドイン

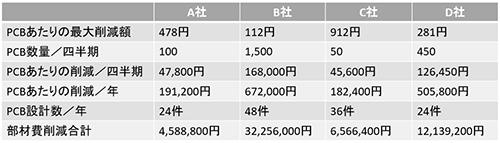

9. 最適なパネル設計による基板製造部材費の削減

エレクトロニクス業界では、単なるDFMを超えるツールが必要になっているが、その証として、『Valor NPI』はPCBパネル設計の最適化にも使用されている。

『Valor NPI』では、実装パネルを容易に作成し、必要なすべての要素(レール、ツーリングホール、フィデューシャル、配線、Vカットなど)を含めることが可能になっている。

実装パネル内でボードを自動的に最適化して、基板製造の部材費を最小限に抑えることもできる。

エレクトロニクス製品の製造コストのなかで基板製造の部材費は見落とされがちだが、大きく削減できる余地がある。

異なる4つの設計企業を対象とした調査を行った結果、パネルを最適化すると1顧客あたり平均で1年あたり約1,380万円削減できることが分かった。

図7 基板製造部材費の削減

さらに、実装アレイにDFM解析を実行すると、単独の基板の段階では特定できないような潜在的な製造問題も特定することができる。

たとえば、ミシン目がSMDパッドに近すぎる問題や、デバイスがPCBの端から張り出し認識カメラによるグローバルフィデューシャルへのアクセスを妨げている問題も特定可能である。

10. まとめ

設計と製造の分業化がよりいっそう進むなか、他社との差別化を図り、可能な限りの時間と費用、コストを削減するには、上流側での効果的な問題解決の実現や、製造サプライヤとのコミュニケーションを体系的に合理化することが差し迫った課題となる。

『Valor NPI』は、設計と製造をシームレスにつなぐインテリジェントなDFMソリューションとして、その効果的な解決策となる。

![【見どころ】「第14回 高機能素材 Week[大阪]」 【見どころ】「第14回 高機能素材 Week[大阪]」](https://jpcb.jp/upload/pickup/M/02757_1776314842.png)